Generate SystemVerilog DPI Components for Simulation with Synopsys VCS

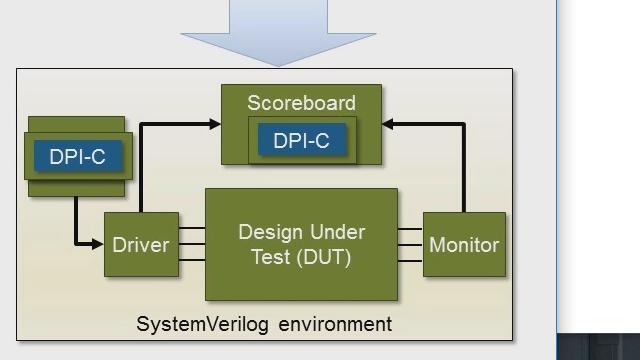

Functional verification is typically the bottleneck of ASIC and FPGA projects, and testbench creation is a large part of that. SystemVerilog DPI component generation in HDL Verifier™ directly exports MATLAB® functions and Simulink® models that can easily plug into a SystemVerilog verification environment.

This example starts with an image processing design in MATLAB, which would be very complex to write models for and require high-performance simulation. HDL Verifier is used to generate SystemVerilog DPI components for use in a Universal Verification Methodology (UVM) environment with Synopsys VCS® simulation and Synopsys Verdi® debugging.

Published: 25 May 2017