cgsl_0413: Reuse memory between component state and output for component deployment

| ID: Title | cgsl_0413: Reuse memory between component state and output for component deployment | |

|---|---|---|

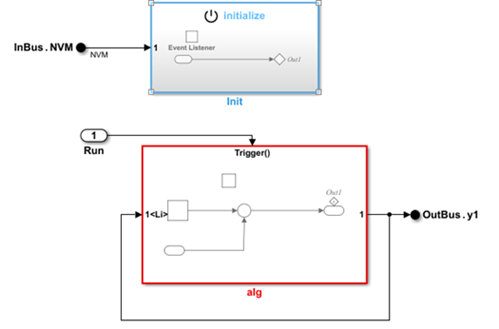

| Description | To optimize component memory usage by reusing memory for state and output data, use one of these methods: | |

| A | Use a function loopback pattern to model the state variable as a signal. | |

| B | Use a Delay block to model the state variable explicitly. Set the state of the Delay block and the function output port to the same literal initial condition value. | |

| Notes | This approach is applicable for data communication methods Outside Execution and Direct Access because these methods can access persistent memory. For method B, the code generator makes a best effort to optimize memory usage. Under some conditions, such as when initialization is done dynamically by using a signal rather than a parameter, the code generator might not apply the optimization. If the optimization does not occur, consider using method A. Regardless of whether you use approach A or B, the code generator implements robust handling of data access by functions that execute concurrently. | |

| Rationale | A | Reuse of memory for state and output data. Optimization survives dynamic initialization. |

| B | Reuse of memory for state and output data. | |

| Model Advisor Check | A Model Advisor check is not provided for this guideline. | |

| Examples |

In this example, the data communication method is set to "Direct Access". void CD_accumulator(void)

{

int32_T i;

for (i=0; i<10; i++) {

Out[i] += In[i];

}

} In this example, the data communication method is set to "Outside Execution". void CD_accumulator(void)

{

real_T tmpIrvRead[10];

int32_T i;

tmp = set_CD_accumulator_her_out_y();

for (i=0; i<10; i++) {

tmp[i] = (get_CD_accumulator_DataTransfer(tmpIrvRead))[i] + tmp[i];

}

} | |

See Also

Code Interfaces and Code Interface Specification (Embedded Coder)

Service Interfaces (Embedded Coder)

Embedded Coder Dictionary (Embedded Coder)

Data Communication Methods (Embedded Coder)

Use dynamic memory allocation for model initialization (Embedded Coder)