Read Position of BiSS-C Absolute Encoder

This example shows how to read a position of an absolute encoder using the bidirectional serial/synchronous-continuous (BiSS-C) open protocol in the unidirectional mode. This example implements the BiSS-C protocol using TI C2000 peripherals such as CLB, SPI, ePWM, X-BAR, and GPIO using the C2000™ Microcontroller Blockset.

Using this example, you can:

Configure peripheral modules such as CLB, SPI, ePWM, X-BAR, and GPIO to design and implement a BiSS-C protocol.

Generate code for the controller and load it on the hardware board.

Perform Monitor & Tune to monitor the position signals on the host computer.

BiSS-C Interface

BiSS-C mode (unidirectional) is a fast synchronous serial interface for acquiring position data from an encoder. The controller controls the time of position acquisition and the data transmission speed, and the encoder transfers the position data to the controller.

The interface consists of two unidirectional differential pairs of lines:

Controller clock signals (represented as MA in the diagram) transmits position acquisition requests and timing information (clock) from controller to encoder.

Encoder data out (represented as SLO in the diagram) transfers position data from encoder to controller, synchronized to MA.

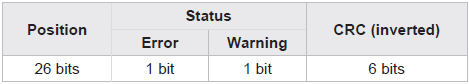

This diagram shows the data format for BiSS-C protocol.

Introduction

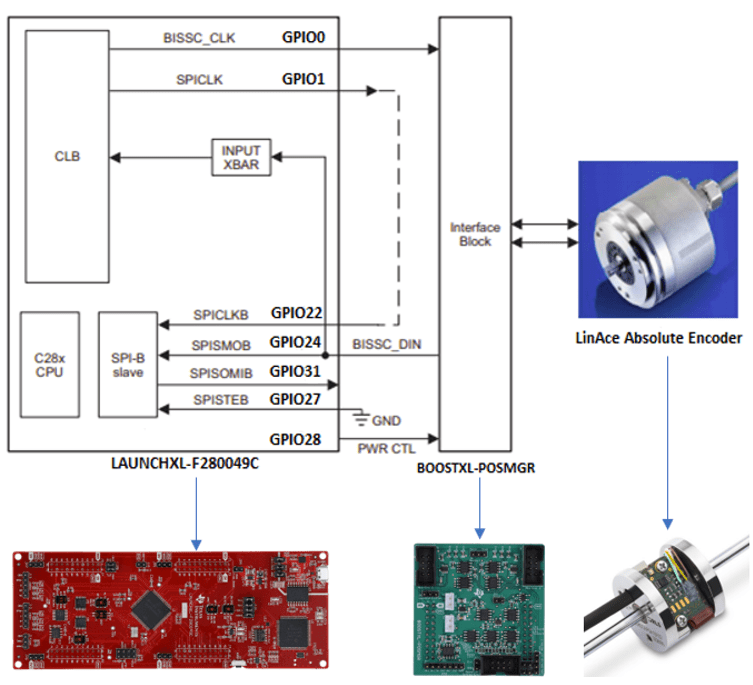

BiSS protocol implemented TI C2000 F280049C MCU through TI BOOSTXL-POSMGR Position Manager Booster Pack is used to interface the linear shaft absolute encoder from LinAce. Communication over BiSS-C interface is achieved primarily by CPU (C28x), configurable logic block (CLB), serial peripheral interface (SPI), and device interconnects (X-BARs).

CLB is configured to generate the BiSS-C protocol clock signals (BiSSC_CLK and SPICLK).

BiSS-C protocol clock signals are sent through ePWM channels (GPIO0 &1).

SPI performs the encoder data receive functions.

Input X-BAR is configured to enable the CLB to monitor the SPISIMO signal for detecting the start pulse and accordingly adjusts the phase of the receive clock (SPICLK).

Implementation

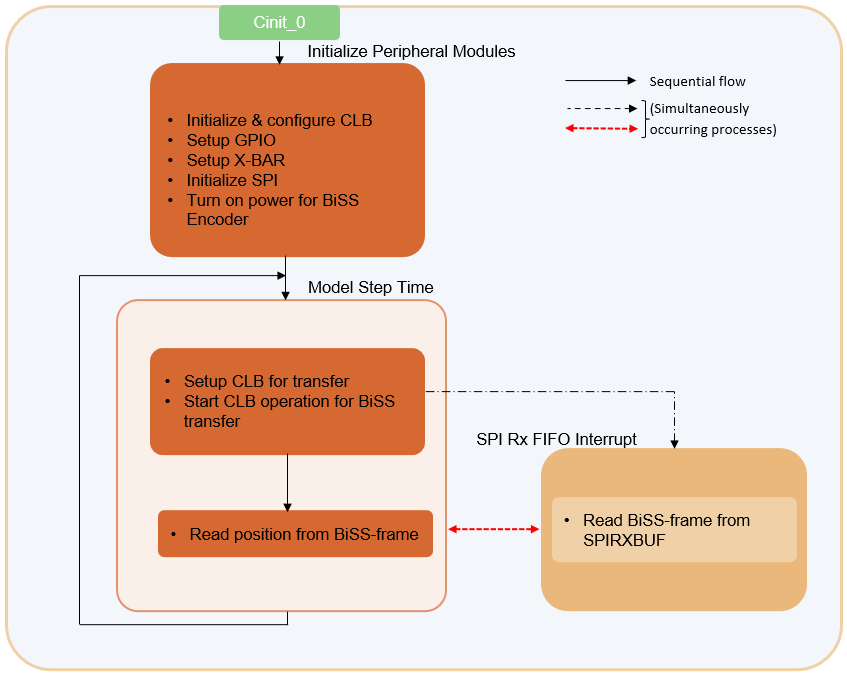

This workflow describes the BiSS-C implementation with respect to the TI F280049C Launchpad.

The CPU sets up a CLB for current BiSS-C command depending on the data packet format of the LinAce encoder as shown here:

At each step time in the model, CPU sets up the CLB operation to generate BiSS-C command to read the encoder position.

CLB TILE3 generates a 2MHz reference clock within the CLB module and number of clock pulses (BiSS_CLK-49 pulses and SPICLK-36 pulses), including the edge placement for these two clocks which is precisely controlled by the CLB TILE1 at this rate.

A SPI interrupt is generated after receiving the data packet from the encoder. CPU then reads and decodes the encoder position from the SPI Receive FIFO.

Required Hardware

5V external power supply

Micro-USB cable

Available Models

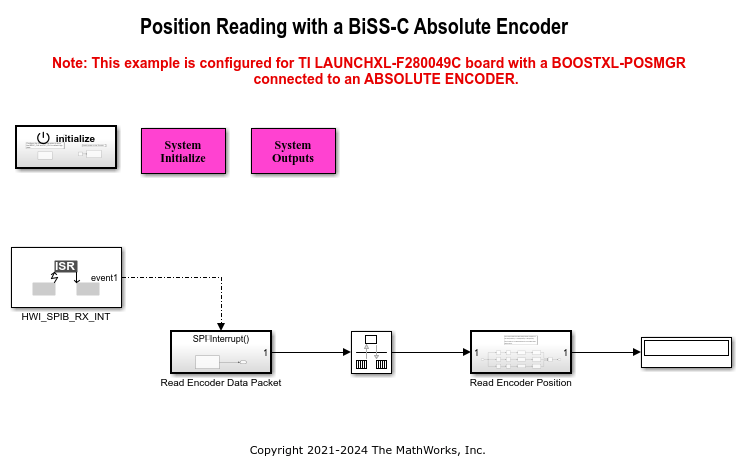

You can use the f280049C_BiSSC_Protocol.slx to generate code and load it on the F280049C LaunchPad.

Hardware Connections

Connect the Texas Instruments Piccolo F280049C LaunchPad to Texas Instruments BOOSTXL-POSMGR. For more information, refer to Connect F280049C LaunchPad to BOOSTXL-POSMGR.

Connect the Texas Instruments BOOSTXL-POSMGR to BiSS-C Absolute Encoder. For more information, refer to Connect BOOSTXL-POSMGR to Absolute Encoder.

Encoder Connections. For more information, refer to Encoder Connections.

Model

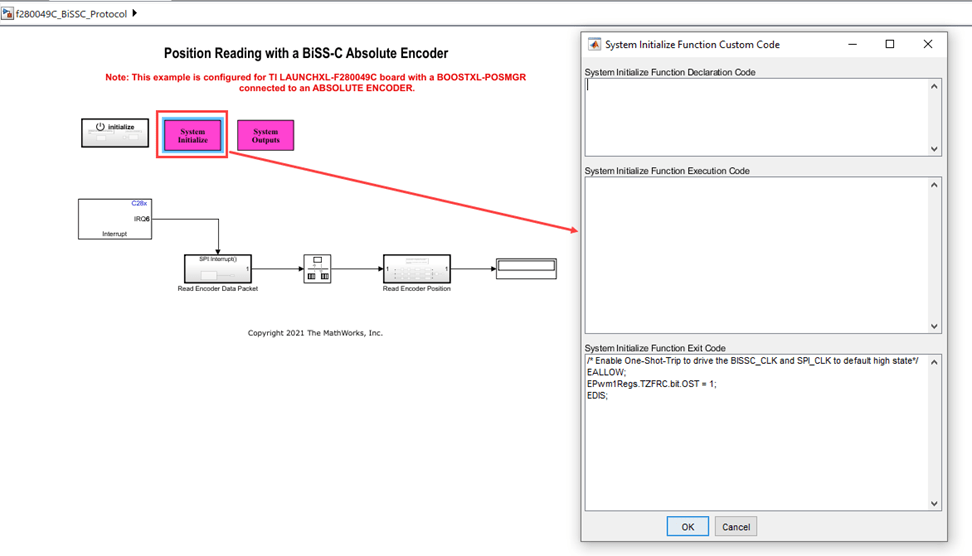

Open the f280049C_BiSSC_Protocol.slx model.

This example demonstrates how to generate the BiSS-C command from the MCU (Controller) to read the position values from the encoder.

Task 1 - Configure and Run Position Reading with a BiSS-C Absolute Encoder Model

1. Open the f280049C_BiSSC_Protocol.slx model. This model is configured for TI Piccolo F280049C LaunchPad hardware.

2. To run the model on other TI C2000 processors, first press Ctrl+E to open the Configuration Parameters dialog box. Then, select the required hardware board by navigating to Hardware Implementation > Hardware board.

Note: Ensure that the BOOSTXL-POSMGR is connected to the selected hardware board with correct pin mappings.

3. Perform the peripherals configurations in the model as shown in the Task 2. You can use the same parameter values if you want to run this example for other hardware boards.

Task 2 - Peripheral Configurations

Set the peripheral block configurations for this model. Double-click the blocks to open block parameter configurations. You can use the same parameter values if you want to run this example on other hardware boards.

CLB Tile, CLB X-BAR, Input X-bar, ePWM are configured to generate BiSS Clock and SPI clock.

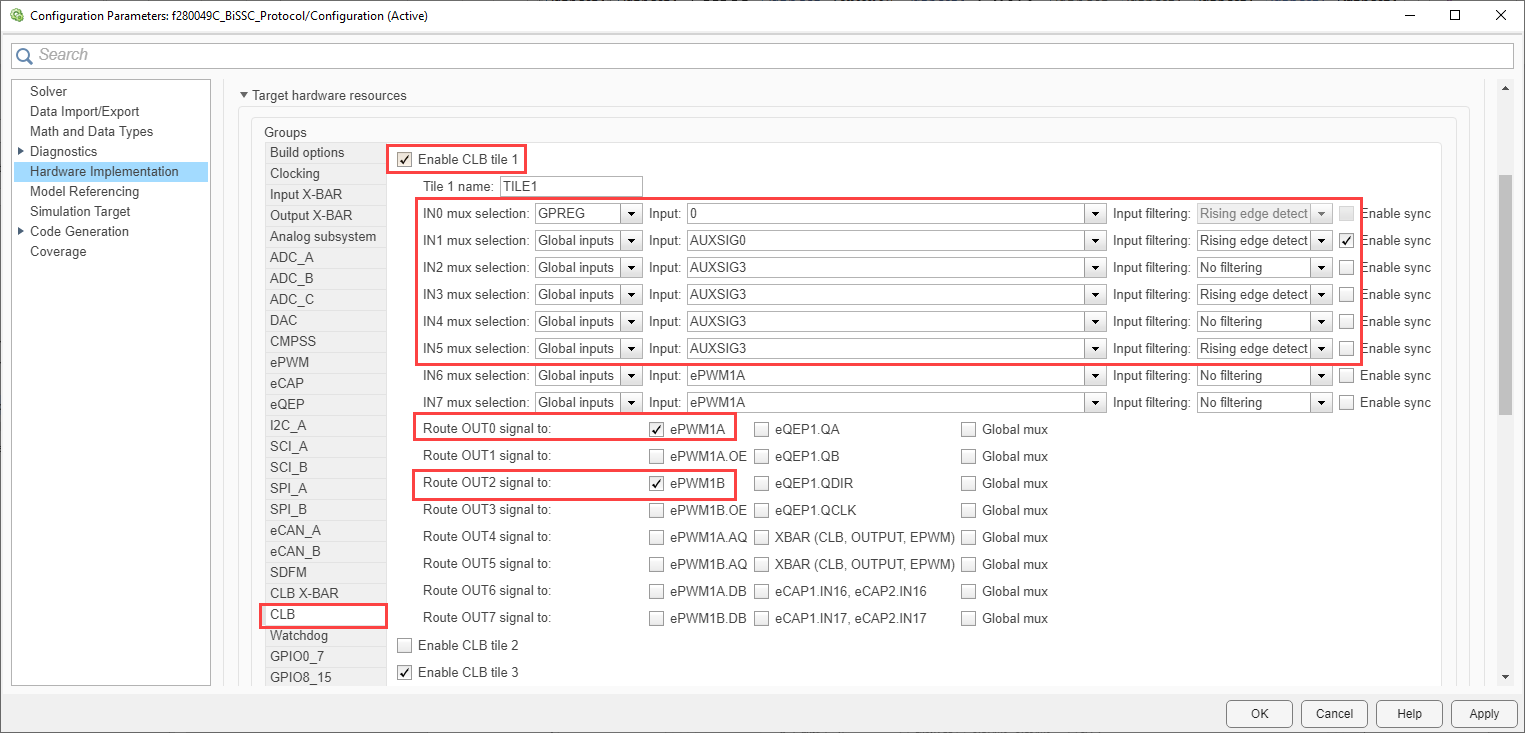

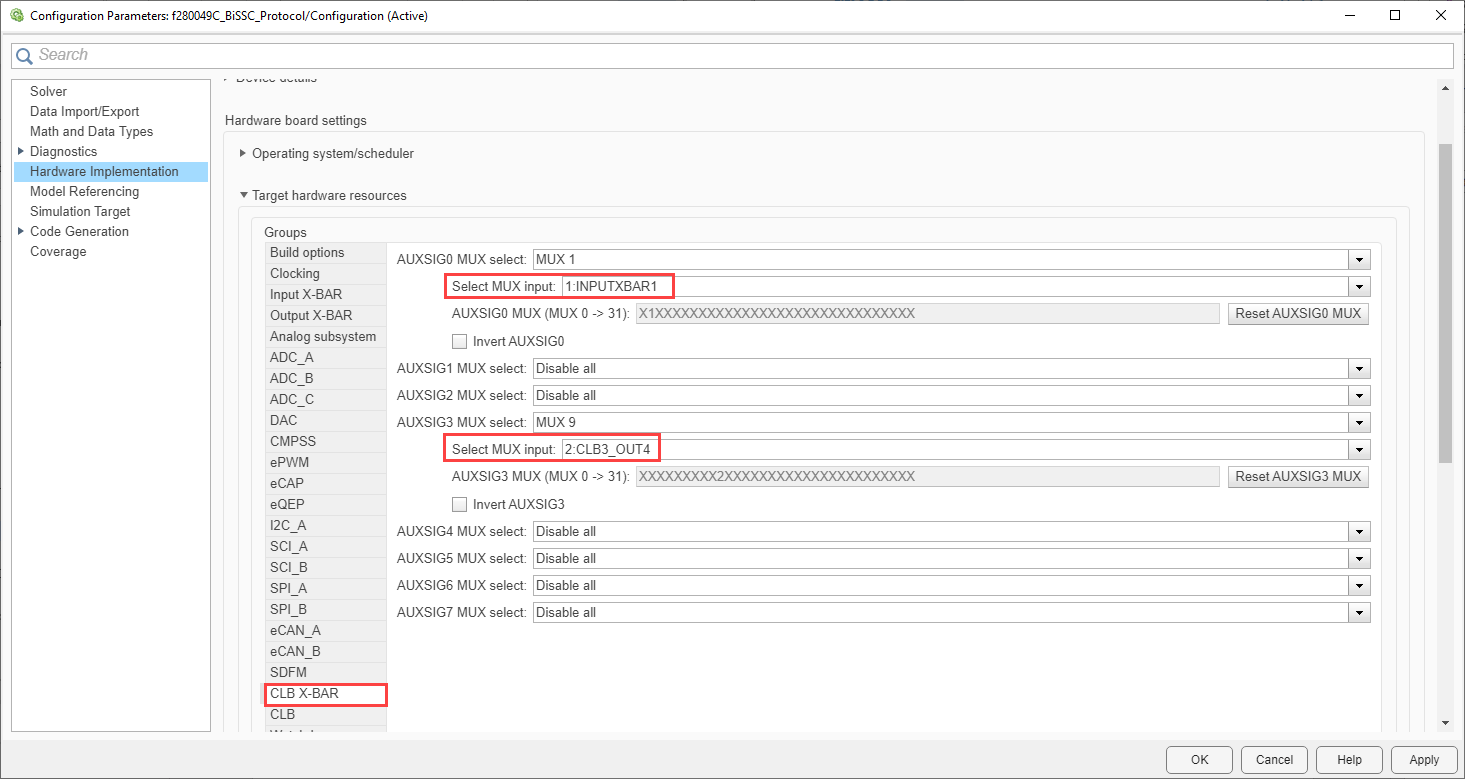

CLB

For CLB Tile 1:

Configure GPREG for Tile boundary IN0 to control the clock generation sequence.

The generated BISSC_CLK and SPICLK clock outputs generated on TILE1 are routed to the ePWM1A and ePWM1B output pins. The remaining tile boundary configurations are explained in the subsequent sections.

For CLB Tile 3:

GPREG settings for TILE3 boundary IN0

TILE3 OUT4 is routed to Global Mux which then is configured in CLB X-BAR to be used by TILE1.

The CLB configuration files, that is the header file and the source file generated from the CCS CLB config tool, are imported into the Simulink model. For more information on how to configure the header file and the source file, For more information, see CLB Logic for Clock Generation.

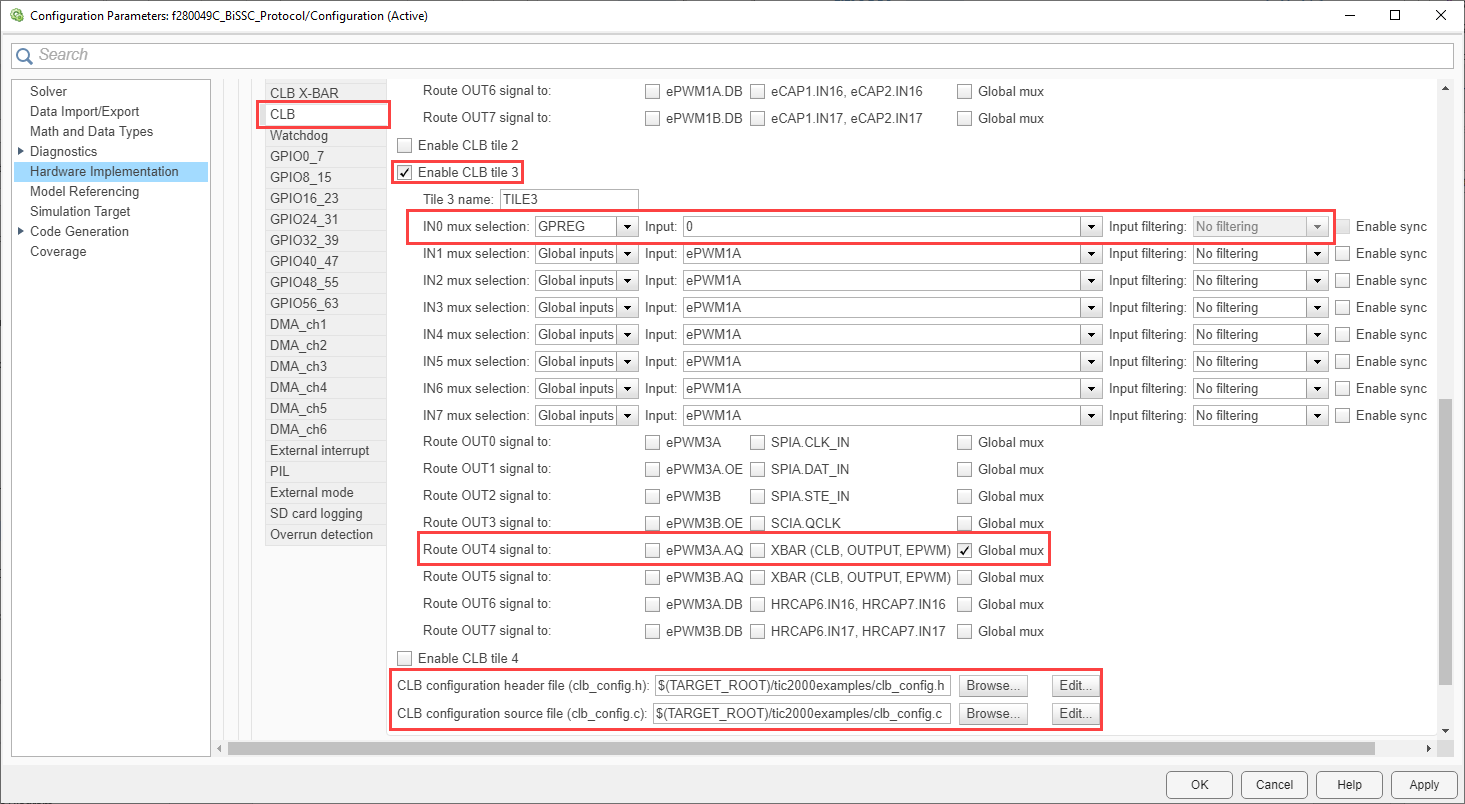

CLB X-BAR

AUXSIG0 Mux select is configured to connect the INPUTXBAR1 i.e BISSC_DIN line to the input of the TILE1 BOUNDARY IN1.

AUXSIG3 Mux select is configured to connect the CLB3_OUT4 (clock source of 2MHz for TILE1) to the input of the TILE1_BOUNDARY in2, in3, in4 and in5.

Input X-BAR

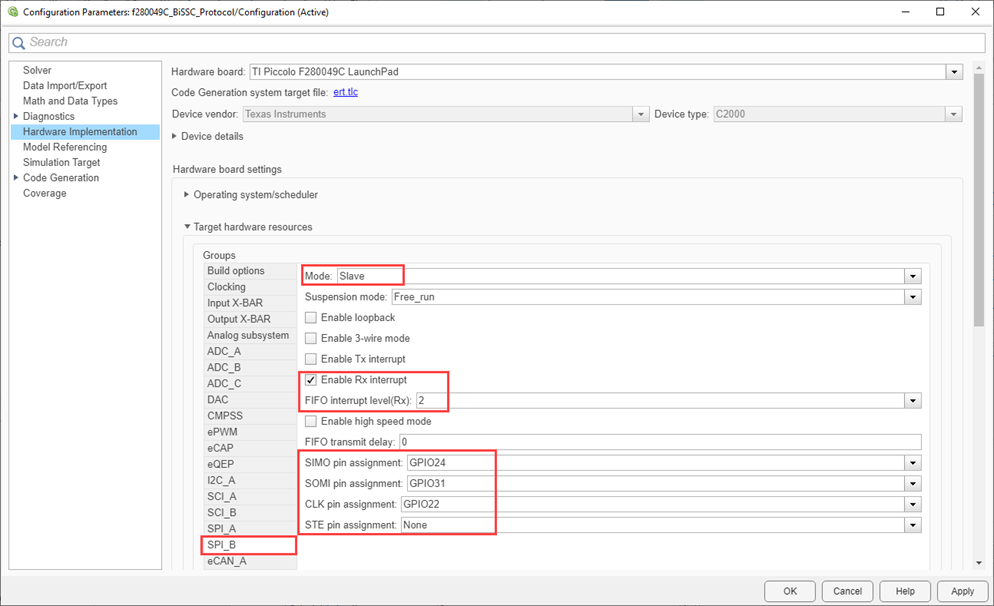

SPIB_SIMO on GPIO24(BISSC_DIN) line over which encoder response is generated is configured in INPUT X-BAR INPUT1.

This setting enables encoder start pulse to be read inside TILE1 by the TILE1_FSM_1 followed by TILE1_FSM_2 to trigger the TILE1_COUNTER_2 to generate the SPICLK clock cycles to read the data packet.

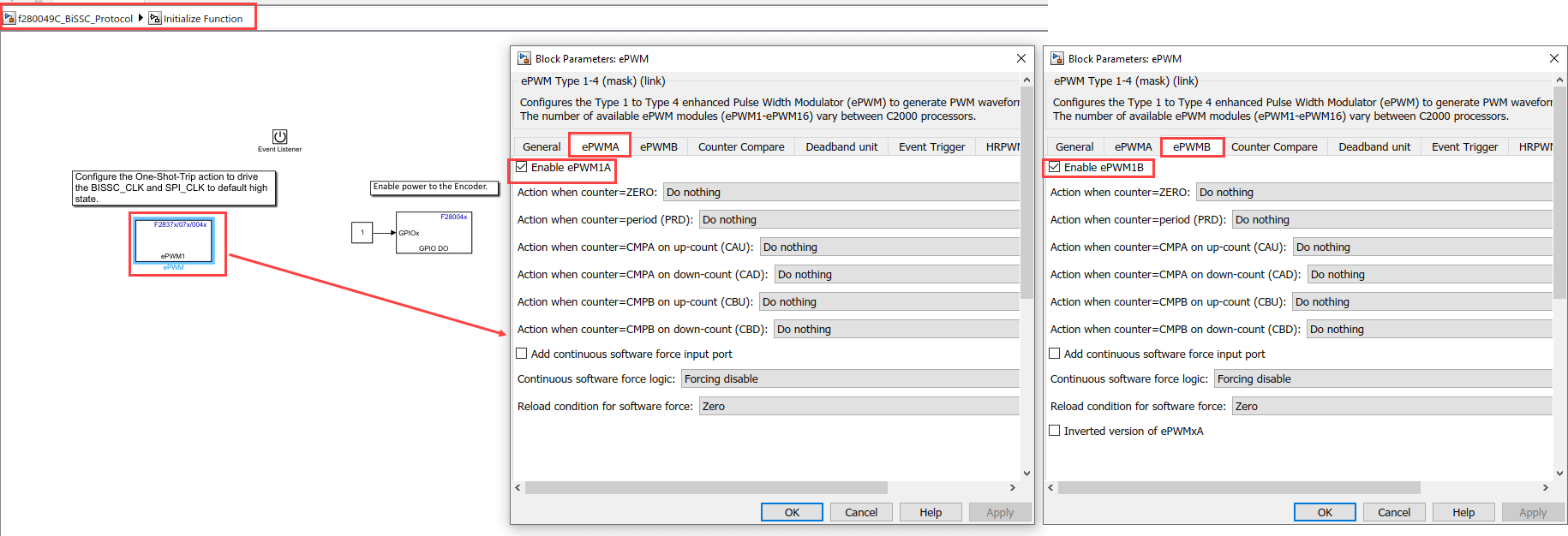

ePWM Block

Configure ePWM One Shot Trip option to drive the outputs GPIO0 (ePWM1A) and GPIO1 (ePWM1B) to high state i.e the idle state for the output.

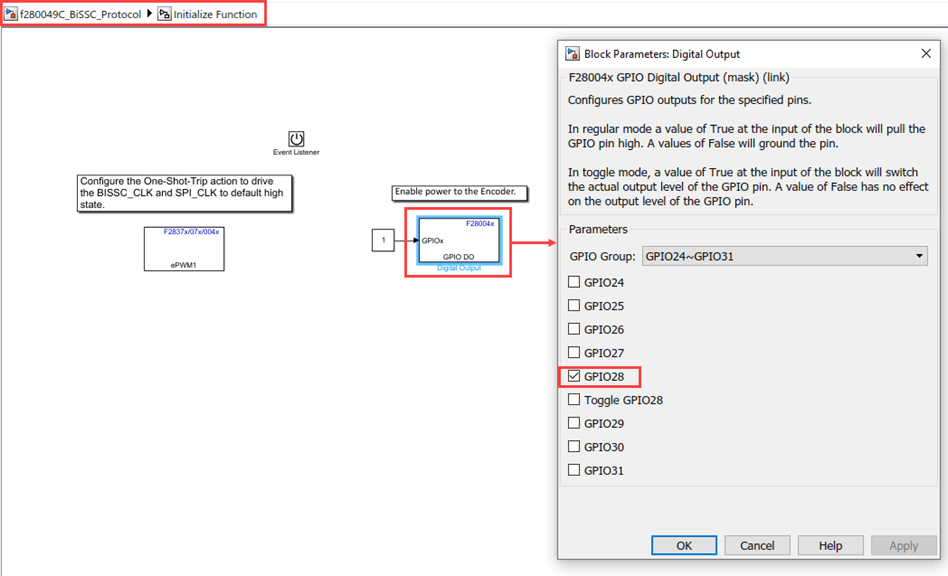

GPIO Block

Enable the power to the encoder. Configure the GPIO28 output pin High to drive the encoder.

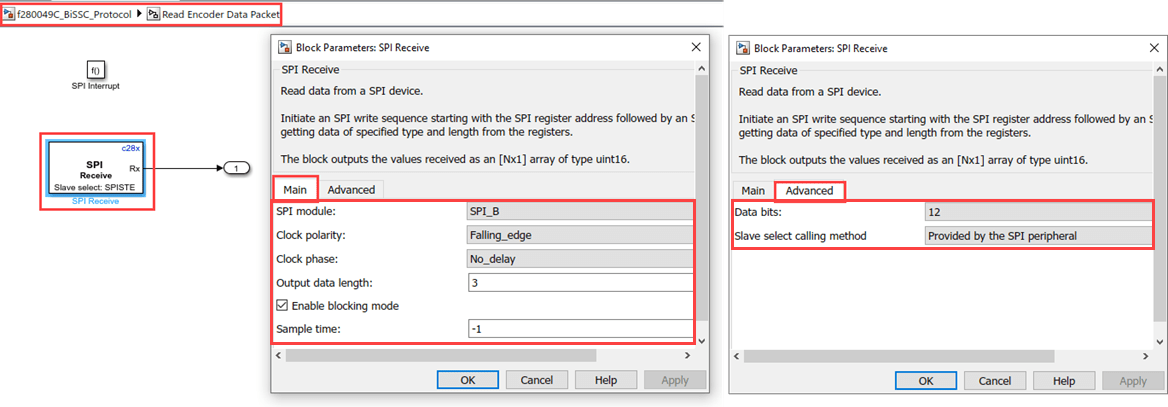

SPI Block

Configure the SPI block to read the encoder position.

Note: For SPI configuration, the STE pin on the BOOSTXL-POSMGR is connected to ground. Hence the pin is uninitialized from MCU.

Task 3 - CLB Logic for Clock Generation

In this task you will learn how to:

UpdateorModifythe CLB Tile configurations. For more information, see CLB Tile Configuration.Generate CLB configuration file. For more information, see Generate CLB Configuration File.

Generate CLB configuration HTML file. For more information, see Generate CLB Configuration in HTML.

Task 4 - Monitor Signals and Tune the Model

When you perform Monitor & Tune action for the model, the host computer communicates with the target on which the generated executable runs.

Note: The following Monitor & Tune steps are demonstrated using TI F2806x hardware. To perform Monitor & Tune on the TI F280049C LaunchPad, follow the same configuration shown below.

Prerequisites

Before executing Monitor & Tune, perform the following SCI configuration and Dip switch configuration.

SCI Configuration

As GPIO28 is used to enable the power to the encoder, use GPIO 35 or GPIO37 for UART to run the external mode.

Dip Switch Configuration

Configure the dip switch to the following:

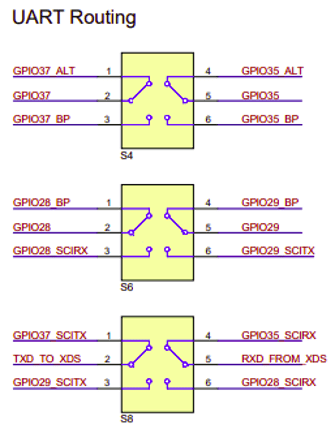

1. Dip switch S3, S4, S8: GPIO35 and GPIO37 routed to the virtual COM port for external mode operation.

2. Dip switch S6: Route the GPIO28-29 to BoosterPack Header. GPIO28 now enables the power to Encoder.

1. Open the Hardware tab and click Monitor & Tune. You can observe from the Diagnostic Viewer that the code is generated for the model and the host connects to the target after loading the generated executable.

Monitor Signals

While the model runs, you can monitor the following signals on the Display block. You can monitor the position counts of absolute encoder in the Display block.

Other Things to Try

Try to run the example on F28379D target and analyze the results.

BOOSTXL-POSMGR supports interfacing up-to 2 encoders. A second encoder can be interfaced with the similar approach.

Perform Cyclic Redundancy Check(CRC) on the position data.