Modeling Control Law Accelerator (CLA) Using Model Reference

The control law accelerator (CLA) is a coprocessor that supports parallel processing. Using the CLA for time-critical tasks frees up the other CPUs to perform other system- and higher-level asynchronous tasks concurrently. The CLA coprocessor also can directly connect to the hardware peripherals, such as analog-to-digital-conversion (ADC) and pulse-width-modulation (PWM), to minimize latency in time-critical tasks.

Configure C2000 Model with CLA Coprocessor

A C2000™ processor with a CLA coprocessor consists of a Task Manager or CLA Task Manager block and reference Model blocks containing the tasks for execution on each processor in the system. This model contains sample models of the C2000 processor, and CLA processor each with an event-driven task.

Note

Models using CLA requires long long mode to be set to

off.

Configure C2000 Top-Level Model

Open a new Simulink model. Save the model as

tif2838xD_top.slx.Configure the

tif2838xD_top.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

None.Click Finish.

Configure C2000 Processor Model

Open a new Simulink model. Save the model as

tif2838xD_c28xCPU1.slx.Configure the

tif2838xD_c28xCPU1.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

c28xCPU1.Click Finish.

Add the event- and timer-driven tasks to the C2000 processor model.

In the

tif2838xD_top.slxmodel, add CLA Task Manager and Model blocks.Assign the

tif2838xD_c28xCPU1.slxmodel to the Model block and then connect the tasks to the Task Manager block.

Configure CLA Coprocessor Model

Open a new Simulink® model. Save the model as

tif2838xD_CLA.slx.Configure the

tif2838xD_CLA.slxmodel to be a C2000 application.Open the Modeling tab and press Ctrl+E (Model settings) to open Configuration Parameters dialog box.

Go to Hardware Implementation > Hardware board and select TI F2838x.

In the Hardware board settings> Processing unit, select

CPU1CLA1.Click Finish.

Add event-driven tasks to the CLA model.

In the

tif2838xD_top.slxmodel, add CLA Task Manager and Model blocks.Assign the

tif2838xD_CLA.slxmodel to the Model block and then connect the tasks to the CLA Task Manager block.

The CLA coprocessor has restricted regional memory access. In code generation and deployment to the hardware board, the tasks automatically get mapped to the appropriate sections in the CLA ROM. You can inspect the memory sections for inports, outports, signals, states, and internal data assigned using the Code Mappings Editor — C (Embedded Coder) tool in the CLA reference model.

Configure C2000 Model with CLA Coprocessor

This example shows how to create a C2000 model that contains the C2000 processor and the Control Law Accelerator (CLA) coprocessor. The C2000 processor model contains a timer-driven task that executes every 0.1 seconds. The CLA coprocessor model contains a task driven by events from the ADC, modeled by the ADC Read (SoC Blockset) and ADC Interface (SoC Blockset) block pair. Open the model.

open_system("c2000_and_cla_setup_top_level_model.slx")

Run the model and inspect the task execution in the Simulation Data Inspector. As separate processors, the tasks run without Interfering with each other's execution.

Note: When you try to build the model, ensure that the Code generation folder structure parameter is set to Target environment subfolder.

Run the following API in the MATLAB command prompt to set the Code generation folder structure parameter to Target environment subfolder.

cfg = Simulink.fileGenControl('getConfig');

cfg.CodeGenFolderStructure = 'TargetEnvironmentSubfolder';

Simulink.fileGenControl('setConfig', 'config', cfg);

Alternatively, open the model. Navigate to Modeling tab > Environment > Simulink Preferences > General and set Code generation folder structure parameter to Target environment subfolder.

Link Task Execution Using Software Triggers

The CPU can use software interrupts to launch tasks on the CLA coprocessor using the Software Trigger CPU<->CLA block. You can use this block to launch specified tasks from the C2000 on the processor, which frees up the C2000 processor to act in a supervisory role during system execution. The Software Trigger CPU<->CLA can also be used inside the CLA to launch tasks on the CPU.

You can add an Software Trigger CPU<->CLA to the CPU to launch tasks on the CLA by following these steps.

Choose an existing task in the CPU reference model.

Add the Software Trigger CPU<->CLA block inside the task.

Note

The Software Trigger CPU<->CLA block must be in an atomic subsystem block for periodic tasks.

Connect the input to a boolean signal. You can specify the Software Trigger CPU<->CLA block to trigger on a rising edge or when the signal is high.

Connect the output to an Outport block.

In the Software Trigger CPU<->CLA block, set the Task number to the CLA task.

In the CPU reference model, select the Outport block that connects the Software Trigger CPU<->CLA block to the top-level soc model.

In the Signal Attributes panel, refresh the Data type choices by choosing

–-- Refresh Data Types –--. Then set Data type toBus: rteEvent.Select Output as nonvirtual bus in parent model.

Click OK to apply the changes to the Outport block.

In the top-level model, connect the message output from the C2000 reference model to the CLA Task Manager block.

Note

The assigned task must match the task number specified in the Software Trigger CPU<->CLA.

Exchange data between the two processors using the Interprocess Data Read, Interprocess Data Channel, and Interprocess Data Write block triplet. The block triplet simulates the

exchange of data between the C2000 processor and the CLA coprocessor. When the model

generates code, interrupts in the ePIE table with data being

transferred through shared memory, such as the LS, replace the block triplet for the specified C2000 processor.n

RAM

Synchronization Between CPU and CLA Coprocessor

This example shows how to launch tasks on the control law accelerator (CLA) coprocessors from the C2000 processor. The C2000 processor can launch tasks on the CLA coprocessor using the Software Trigger CPU<->CLA block. This model shows a timer-driven task on the C2000 processor that triggers and executes a CLA task on the CLA.

Data Exchange Between CPU and CLA Coprocessor

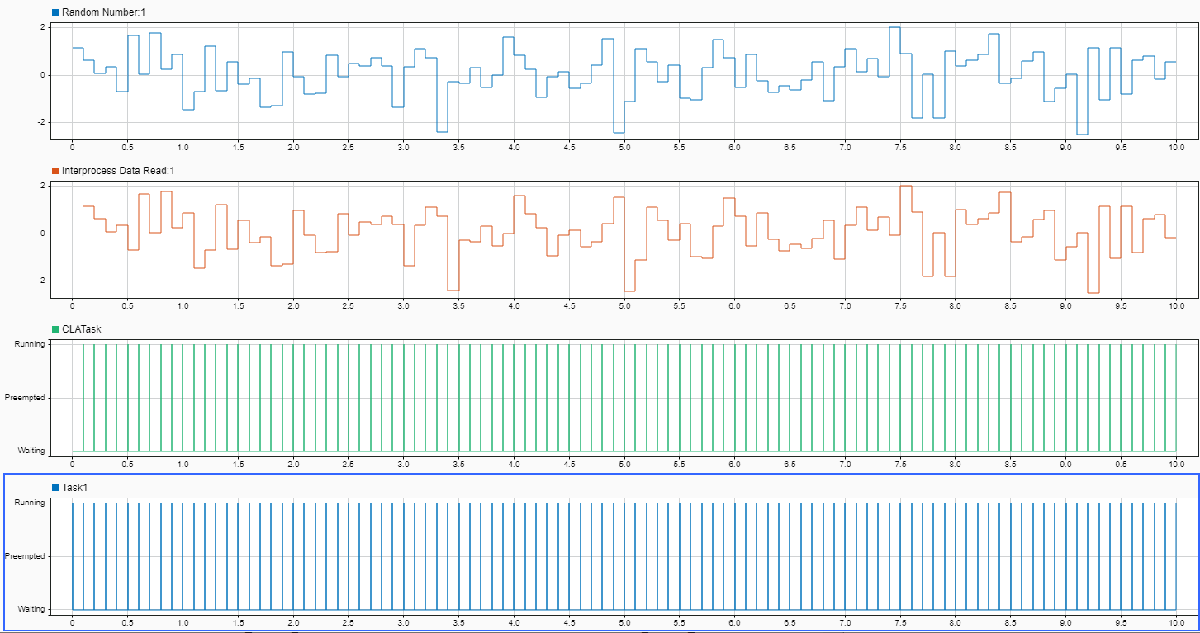

This example shows the basic connections available to transfer data between the C2000 processor and CLA coprocessors. The C2000 processor and CLA coprocessor can share data with the Interprocess Data Channel (SoC Blockset), Interprocess Data Read (SoC Blockset), Interprocess Data Write (SoC Blockset) blocks. This model shows a timer-driven task, driven by the Task Manager (SoC Blockset) block, on the C2000 processor that transmits a random number over the Interprocessor Data Channel block to the CLA coprocessor. When the CLA processor receives the data, the CLA Task triggers and reads the data packet.

open_system("CPU_to_CLA_synchronization_top_level_model");

This figure shows the Simulation Data Inspector view of the tasks in the applications where the CPU task, Task1, triggers the CLATask.

This figure shows the Simulation Data Inspector view of the data and tasks in the applications. The delay between the CPU and CLA measurements are due to CPU completing transmission and the start of the CLA task.

See Also

Task Manager | CLA Task Manager | Software Trigger CPU<->CLA | Interprocess Data Read | Interprocess Data Channel | Interprocess Data Write