viaSingleEnded

Description

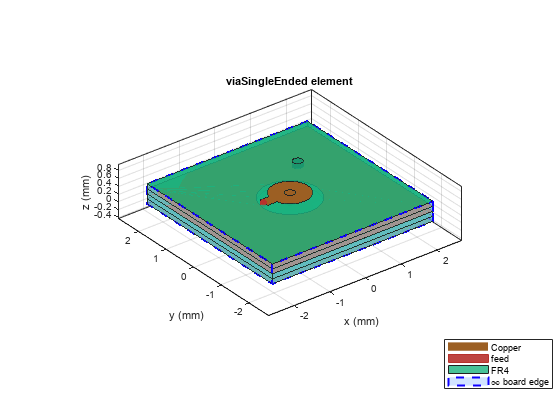

Use the viaSingleEnded object to create a single-ended via model

within a printed circuit board (PCB) stack.

A vertical interconnect access (via) is an essential part of a multilayer PCB. You can use vias to create an electrical connection between the different layers in a PCB. You can construct vias by placing copper pads on each layer of the PCB and drilling a hole through the pads, using a non-conductive material in the inner layer of the via and a conductive plating on the outer layer.

A via consists of:

Barrel — Conductive tube filling the drilled hole

Pad — Connects each end of the barrel to a component, plane, or trace

Antipad — Clearance hole between the barrel and metal layer

In a multilayer PCB, vias reduce the length over which you need to route a trace to complete its connection. Smaller the via, the better the performance of the circuit.

Note

In this release, viaSingleEnded only supports behavioral model analysis

of s-parameters. For more information, see Behavioral Models.

Creation

Syntax

Description

via = viaSingleEnded creates a single-ended via with default

properties. This via has four dielectric layers, two signal layers, three ground layers,

one signal via, and one ground return via. The default substrate is FR4 with a thickness

of 1.27e-4 m per layer.

via = viaSingleEnded(number of conductive layers) returns a

single-ended via based on the number of conductive layers. The expected number of

conductive layers must be two, or greater.

via = viaSingleEnded(

sets Properties using one or more

name-value arguments. For example,

PropertyName=Value)viaSingleEnded(SignalViaDiameter=0.0065) creates a single-ended via

with a signal diameter of 0.0065 meters. Properties not specified

retain their default values.

Properties

Object Functions

criticalwavelength | Number of wavelengths between signal via and ground return vias |

gapratedistance | Gap rate distance metric |

layout | Plot all metal layers and board shape |

shapes | Extract all metal layer shapes of PCB component |

show | Display PCB component structure or PCB shape |

sparameters | Calculate S-parameters for RF PCB objects |

padsTable | Display pad stack used by viaSingleEnded in a table |

antipadsTable | Display antipads stack used by viaSingleEnded in a tabular

from |

getpads | Generate a pad stack |

getantipads | Generate antipad stack |

Examples

References

[1] Steinberger, Telian, Tsuk, Iyer and Yanamadala, “Proper Ground Via Placement for 40+ Gbps Signaling”, DesignCon 2022, April 2022.

[2] Ramo, Whinnery and Van Duzer, Fields and Waves in Communications Electronics, third edition, section 9.3, John Wiley and Sons Inc., copyright 1994