CPFSK Modulator Baseband

Modulate using continuous phase frequency shift keying method

Libraries:

Communications Toolbox /

Modulation /

Digital Baseband Modulation /

CPM

Description

The CPFSK Modulator Baseband block modulates a signal using the continuous phase frequency shift keying (CPFSK) method. The output is a baseband representation of the modulated signal. For more information about the modulation and the filtering applied, see Algorithms.

Examples

Demodulate a CPFSK-modulated signal impaired by AWGN and compute the bit error rate.

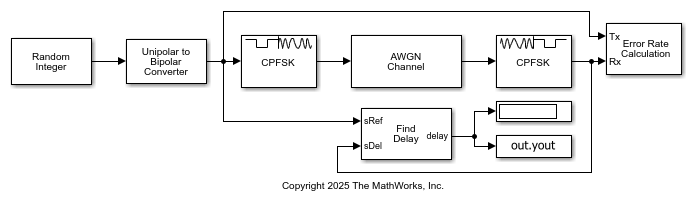

The cm_cpfsk_mod_demod model generates random integer data, converts it to bipolar values, and then applies CPFSK modulation to frames data. The CPFSK-modulated signal passes through an AWGN channel and then is demodulated by using the CPFSK method. The bit error rate is calculated on frames of data.

The Error Rate Calculation block has the receive delay set to the value of the traceback depth used by the CPFSK Baseband Demodulator block. The model uses the Find Delay block to confirm the delay equals the value of the traceback depth.

Transmit to receive delay is 16 symbols. BER = 0.0033255

Nonlinear digital demodulation techniques can be more prone to issues caused by misalignment of symbol boundaries due to their sensitivity to timing errors, increased susceptibility to intersymbol interference (ISI), and potential for introducing nonlinear distortions. For the demodulation to work correctly, the input signal to the demodulator block must have the correct alignment. Various blocks between the modulator and the demodulator introduce processing delays, leading to incorrect alignment. This example shows how to correct this type of misalignment.

Open the Model

The model includes the following blocks:

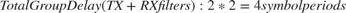

The Bernoulli Binary Generator block generates random binary inputs.

The CPFSK Modulator Baseband and CPFSK Demodulator Baseband blocks use continuous phase frequency shift keying (CFPSK) for modulation and demodulation.

The Raised Cosine Transmit Filter and Raised Cosine Receive Filter blocks to apply pulse shaping by interpolating and decimating the input signal using a raised cosine finite impulse response (FIT) filter.

The AWGN Channel block is for channel modeling.

The Error Rate Calculation block computes the bit error rate.

Adjust Delays

The CPFSK Demodulator block processes each collection of eight samples per symbol to compute one output symbol. For binary CPFSK with a modulation index of 1/2, the demodulator input must align along even numbers of symbols. The requirement applies only to binary CPFSK with a modulation index of 1/2. Other CPM schemes with different M-ary values and modulation indexes have different requirements.

Both the Raised Cosine Transmit Filter and the Raised Cosine Receive Filter introduce a group delay (GD) in the system. Set the Filter Span in Symbols property in both the filters to 2*2 . GD in symbols is half of the filter span which is 2 , and the combined GD is 4.

To ensure that the CPFSK Demodulator block receives the input samples in aligned to the start of the traceback depth specified in the block, you use the Delay block to introduce a delay of 12 samples. In sample-based mode, the CPFSK Demodulator block introduces a delay of Traceback length + 1 samples at its output. With a Traceback length of 16, the total CPFSK Demodulator Delay is 17 and the total receiver delay is 17 + 2 = 19 samples.

Run the Model

When you run the model, you can see:

Evaluate Error Rates

The Error Rate Calculation block shows a minimal error count, indicating an overall low error rate in the system compared to the number of samples evaluated. This outcome results from the absence of alignment issues, ensuring high data integrity and system performance.

To establish a baseline, remove the noise from the system by deleting the AWGN Channel block from the model. The Error Rate Calculation block then reports zero errors.

Observe Effects of Misalignment

In the model, remove the delay block. The demodulator input does not align along even numbers of symbols. Consequently, this misalignment leads to a significant increase in the error rate and the number of errors reported by the Error Rate Calculation block.

Conclusion

Managing delays and alignment ensures data integrity and system performance. By incorporating a delay block to compensate for the misalignment caused by the Raised Cosine Transmit and Receive Filter blocks, you can see that the model successfully aligns the symbol boundaries before the demodulation process and reduces the overall error rates.

Ports

Input

Input signal, specified as a scalar or column vector. For more information, see Integer-Valued and Binary-Valued Input Signals.

Data Types: double | Boolean | int8 | int16 | int32

Output

CPFSK-modulated baseband signal, returned as a scalar or column vector. The modulated output symbols are oversampled by the Samples per symbol parameter value. For information on the processing rates, see Single-Rate Processing and Multirate Processing.

Use the Output data type parameter to specify the data type for the demodulated output signal.

Data Types: double | single

Parameters

To edit block parameters interactively, use the Property Inspector. From the Simulink® Toolstrip, on the Simulation tab, in the Prepare gallery, select Property Inspector.

Modulation order, specified as a power-of-two scalar. The modulation order M = 2k specifies the number of points in the symbol alphabet. k is a positive integer indicating the number of bits per symbol.

Integer or group of bits indicator, specified as Integer or

Bit.

Set this parameter to

Integerto input data as integers.Set this parameter to

Bitto input data as bits.

For more information, see Integer-Valued and Binary-Valued Input Signals.

Symbol mapping of bit inputs, specified as

Binary or Gray.

Set this parameter to

Binaryto map symbols using binary-coded ordering.Set this parameter to

Grayto map symbols using Gray-coded ordering.

For more information, see Integer-Valued and Binary-Valued Input Signals.

Dependencies

To enable this parameter, set Input

type to Bit.

Modulation index {hi}, specified as a nonnegative scalar or column vector. The modulator operates in multi-h. For more information, see CPFSK Modulation Method.

Initial phase offset in radians, specified as a scalar. This property value is the initial phase offset of the modulated waveform.

Symbol sampling rate, specified as a positive integer. This parameter specifies the output symbol upsampling factor for each input sample.

For more information, see Signal Upsampling and Rate Changes.

Block processing rate, specified as one of these options:

Enforce single-rate processing— The input and output signals have the same sample time. The block implements the rate change by making a size change at the output when compared to the input. The output width equals the product of the number of symbols and the Samples per symbol parameter value.Allow multirate processing— The input and output signals have different sample times. The output sample time equals the symbol period divided by the Samples per symbol parameter value.

Data type of the output, specified as double or single.

Block Characteristics

Data Types |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

More About

When you set the Input type parameter to Integer:

The block inputs odd integers in the range [ –(M–1), (M–1)]. M is the modulation order specified by the M-ary number parameter.

The input signal must have a double-precision or signed-integer data type.

When you set the Input type parameter to Bit:

The block inputs groupings of k bits. Each grouping is called a binary word. The input vector length must be an integer multiple of k.

In bit input mode, the block follows this process:

Divide the input bits into k-length bit words and map each to an integer L in the range [0, M – 1], where k =

log2(M) and M is the modulation order specified by the M-ary number parameter. The options for mapping binary words are binary-coded ordering and Gray-coded ordering, as specified by the Symbol set ordering parameter.Map each integer L to signed integers, as 2L–(M–1).

Proceed with modulation processing as in the integer input mode.

The input signal must have a double-precision or

Booleandata type.

In single-rate processing mode, the input and output signals have the same port sample time. In this mode, the input to the block can be multiple symbols. The block implicitly implements the rate change by making a size change at the output when compared to the input.

When you set Input type to

Integer, the input can be a scalar or a column vector with the length equal to the number of input symbols.When you set Input type to

Bit, the input width must be an integer multiple of the number of bits per symbol.

The output width equals NSym × NSPS, where NSym is the number of symbols in the frame and NSPS is the number of samples per symbol, Samples per symbol.

In multirate processing mode, the input and output signals have different port sample times. In this mode, the input to the block must be one symbol.

When you set Input type to

Integer, the input must be a scalar.When you set Input type to

Bit, the input width must equal the number of bits per symbol.

The output sample time equals TSym / NSPS, where TSym is the symbol period and NSPS is the number of samples per symbol, Samples per symbol.

Algorithms

CPFSK modulation is a specific form of continuous phase modulation in which the pulse shaping filter, g(t), has a rectangular pulse of duration, LT=1.

Continuous phase modulation includes a convolutional encoder, a symbol mapper, and a modulator.

The output of the modulator is a baseband representation of the modulated signal:

where:

{αi} is a sequence of M-ary data symbols selected from the alphabet ±1, ±3, ±(M–1).

M must have the form 2k for some positive integer k, where M is the modulation order and specifies the size of the symbol alphabet.

{hi} is a sequence of modulation indices. hi moves cyclically through a set of indices {h0, h1, h2, ..., hH-1}.

When H=1, only one modulation index exists, h0, which is denoted as h. The phase shift over a symbol is π × h.

When hi varies from interval to interval, the modulator operates in multi-h. To ensure a finite number of phase states, hi must be a rational number.

The CPFSK modulation method uses pulse shaping to smooth the phase transitions of the modulated signal. The function q(t) is the phase response obtained from the frequency pulse g(t) through this relation:

.

The specified frequency pulse shape corresponds to this rectangular pulse shape expression for g(t).

L is the main lobe pulse duration in symbol intervals.

The duration of the pulse LT is the pulse length in symbol intervals. For CPFSK modulation, LT=1.

For more information on CPFSK modulation and pulse shape filtering, see [1].

References

[1] Anderson, John B., Tor Aulin, and Carl-Erik Sundberg. Digital Phase Modulation. New York: Plenum Press, 1986.

[2] Proakis, John G. Digital Communications. 5th ed. New York: McGraw Hill, 2007.

Extended Capabilities

C/C++ Code Generation

Generate C and C++ code using Simulink® Coder™.

Version History

Introduced before R2006a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Seleccione un país/idioma

Seleccione un país/idioma para obtener contenido traducido, si está disponible, y ver eventos y ofertas de productos y servicios locales. Según su ubicación geográfica, recomendamos que seleccione: .

También puede seleccionar uno de estos países/idiomas:

Cómo obtener el mejor rendimiento

Seleccione China (en idioma chino o inglés) para obtener el mejor rendimiento. Los sitios web de otros países no están optimizados para ser accedidos desde su ubicación geográfica.

América

- América Latina (Español)

- Canada (English)

- United States (English)

Europa

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)