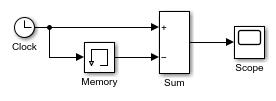

Memory

Generar como salida una entrada de paso de tiempo anterior

Bibliotecas:

Simulink /

Discrete

HDL Coder /

Discrete

Descripción

El bloque Memory retiene y retrasa su entrada por una unidad de tiempo de integración principal. Cuando se coloca en un subsistema iterable, retiene y retrasa su entrada por una iteración. Este bloque acepta señales continuas y discretas. El bloque acepta una entrada y genera una salida. Cada señal puede ser un escalar, un vector, una matriz o un arreglo N-D. Si la entrada no es un escalar, el bloque retiene y retrasa todos los elementos de la entrada durante el mismo paso de tiempo.

Puede especificar la salida del bloque para el primer paso de tiempo con el parámetro Initial condition. Si selecciona este parámetro con precaución, puede evitar un comportamiento de salida no deseado. Aún así, no se puede especificar el tiempo de muestreo. El tiempo de muestreo del bloque se hereda o depende del solver. El parámetro Inherit sample time determina si el tiempo de muestreo se hereda o depende del solver.

Sugerencia

Evite utilizar el bloque Memory cuando estas dos condiciones sean verdaderas:

El modelo utiliza el solver de paso variable

ode15suode113.La entrada al bloque cambia durante la simulación.

Cuando el bloque Memory hereda un tiempo de muestreo discreto, el bloque es análogo al bloque Unit Delay. No obstante, el bloque Memory no admite el registro de estado. Si es necesario registrar el estado final, use un bloque Unit Delay en su lugar.

Comparación con bloques similares

Los bloques Memory, Unit Delay y Zero-Order Hold proporcionan una funcionalidad similar, pero tienen distintas prestaciones. Además, la finalidad de cada bloque es diferente.

Esta tabla muestra el uso recomendado para cada bloque.

| Bloque | Finalidad del bloque | Ejemplos de referencia |

|---|---|---|

| Unit Delay | Implemente un retraso utilizando un tiempo de muestreo discreto que especifique. El bloque acepta y produce como salida señales con un tiempo de muestreo discreto. |

|

| Memory | Implemente un retraso de una unidad de tiempo de integración principal. En condiciones ideales, el bloque acepta señales continuas (o fijas con paso de tiempo secundario) y produce como salida una señal fija con paso de tiempo secundario. |

|

| Zero-Order Hold | Convierta una señal de entrada con un tiempo de muestreo continuo a una señal de salida con un tiempo de muestreo discreto. |

Cada bloque tiene las siguientes características.

| Característica | Memory | Unit Delay | Zero-Order Hold |

|---|---|---|---|

| Especificación de condición inicial | Sí | Sí | No, porque la salida del bloque en la unidad de tiempo t = 0 debe coincidir con el valor de entrada. |

| Especificación de tiempo de muestreo | No, porque el bloque solo puede heredar tiempo de muestreo del bloque controlador o del solver usados para todo el modelo. | Sí | Sí |

| Soporte para señales basadas en tramas | No | Sí | Sí |

| Soporte para registro de estado | No | Sí | No |

Soporte para bus

El bloque Memory es un bloque apto para bus. La entrada puede ser una señal de bus virtual o no virtual sujeta a las siguientes restricciones:

Initial condition debe ser cero, un escalar distinto de cero o una estructura numérica finita.

Si Initial condition es cero o una estructura y especifica State name, la entrada no puede ser un bus virtual.

Si Initial condition es un escalar distinto de cero, no puede especificar State name.

Para obtener información sobre cómo especificar una estructura de condición inicial, consulte Specify Initial Conditions for Bus Elements.

Todas las señales en una entrada de bus no virtual para un bloque Memory deben tener el mismo tiempo de muestreo, incluso si los elementos del objeto bus asociado especifican tiempos de muestreo heredados. Puede usar un bloque Rate Transition para cambiar el tiempo de muestreo de una señal individual o de todas las señales de un bus. Consulte Modify Sample Times for Nonvirtual Buses y Bloques aptos para bus para obtener más información.

Puede usar un arreglo de buses como señal de entrada para un bloque Memory. Puede especificar el parámetro Initial condition con:

El valor

0. En este caso, todas las señales individuales del arreglo de buses utilizan el valor inicial0.Un arreglo de estructuras que especifica una condición inicial para cada una de las señales individuales del arreglo de buses.

Una estructura escalar que especifica una condición inicial para cada uno de los elementos definidos por el tipo de bus. Utilice esta técnica para especificar las mismas condiciones iniciales para cada uno de los buses del arreglo.

Para obtener detalles sobre cómo definir y usar un arreglo de buses, consulte Group Nonvirtual Buses in Arrays of Buses.

Ejemplos

Ejemplos ampliados

Puertos

Entrada

Salida

Parámetros

Características del bloque

Capacidades ampliadas

Historial de versiones

Introducido antes de R2006a