Especificar y verificar requisitos de diseño

Verifique el diseño en base a los requisitos, ajuste contraejemplos utilizando supuestos de entrada

Los requisitos de seguridad definen comportamientos no deseados en un modelo. Simulink® Design Verifier™ utiliza demostración de propiedades para comprobar que las propiedades asociadas a los requisitos del modelo se mantienen con todos los valores de entrada posibles o proporciona contraejemplos que generan infracciones. Puede utilizar Simulink Design Verifier para modelar requisitos de diseño como propiedades y, luego, Prove Properties in a Model.

Bloques

Funciones

Temas

Comenzar aquí

- Prove Model Properties

Workflow and techniques for proving model properties. - Prove Properties in a Model

Prove model properties that you specify using a Proof Objective block. - Use Parameter Table to Find Constraints

An example of how to specify parameters as variables for analysis. - Specify Signal Ranges

Specify the minimum and maximum value that a signal can attain during simulation. Fully specify your design and optimize data types and the generated code by specifying the minimum and maximum value that a signal can attain during simulation. - Minimum and Maximum Input Constraints

An overview of how the Simulink Design Verifier analysis considers specified input minimum and maximum values. - Specify Input Ranges on Simulink and Stateflow Elements

Describes how the analysis handles minimum and maximum values on Simulink and Stateflow® elements. - Verify and Validate a Model and Code

Define requirements, test models and code, check for design errors and standards compliance, and measure test coverage.

Modelado de requisitos para verificación y validación

- Specify Input Ranges on Simulink and Stateflow Elements

Describes how the analysis handles minimum and maximum values on Simulink and Stateflow elements. - Use Specification Models for Requirements-Based Testing

Follow a systematic approach to verify your design model against requirements. (Desde R2022b)

Verificación mediante demostración de propiedades

- Prove Properties in a Model

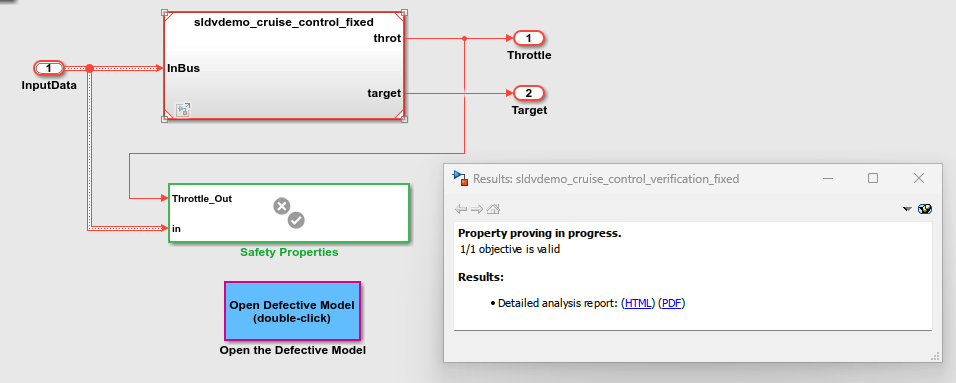

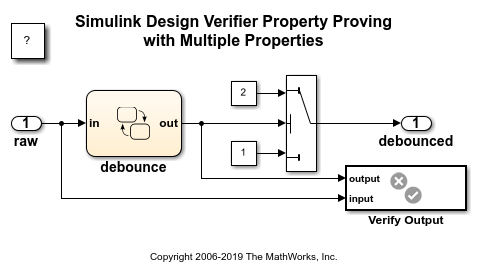

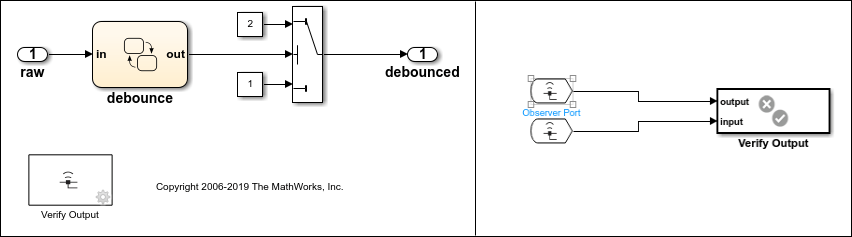

Prove model properties that you specify using a Proof Objective block. - Property Proving Using Proof Objective Block

You can use Simulink® Design Verifier™ to model design requirements as properties and then prove properties in a model. - Debug Property Proving Violations by Using Model Slicer

Use Model Slicer to debug your design with assertion blocks. - Prove System-Level Properties Using Verification Model

An example that uses a verification model to prove system-level properties. - Check for Specified Minimum and Maximum Value Violations

Describes how to analyze the model to verify that specified design minimum and maximum values are honored. - Property Proving Using MATLAB Function Block

This example shows how to verify the seat belt reminder design model. - Property Proving Using MATLAB Truth Table Block

This example shows how to verify the seat belt reminder design model referenced in the top block above. - Property Proving with an Assumption Block

This example shows how to perform a Simulink® Design Verifier™ property proof using a Proof Assumption block. - Property Proving with an Invalid Property

This example shows how to find an invalid property using Simulink® Design Verifier™ property proving analysis. - Prove Properties in Large Models

Use Simulink Design Verifier workflows and best practices for proving properties in large models.